Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

2024-04-01

À l'heure actuelle, les servomoteurs dans les machines-outils CNC domestiques sont généralement équipés de codeurs incrémentiels, tandis que la précision des encodeurs incrémentiels n'est pas trop élevée et la sortie est des signaux parallèles. Pour améliorer sa précision, il est nécessaire d'augmenter la conception de l'encodeur. Difficulté et augmenter la sortie des signaux parallèles, qui n'est pas propice à la communication longue distance entre l'unité servo et l'encodeur. L'encodeur absolu est utilisé, sauf que sa précision est plusieurs fois plus élevée que celle de l'encodeur incrémentiel. La communication série à grande vitesse économise les lignes de communication pour la communication à longue distance. À l'autre extrémité de l'encodeur, le CPLD et l'encodeur absolus sont utilisés pour la communication série à grande vitesse. Le CPLD convertit ensuite les informations du codeur reçues en transmission de données parallèles. Le DSP de l'unité servo effectue un contrôle arithmétique. Cet article donnera la conception du logiciel et du matériel de la communication série à grande vitesse entre CPLD et l'encodeur absolu .

conception matérielle

Le matériel est principalement composé de trois modules: l'alimentation, le CPLD et ses circuits périphériques et le circuit d'interface du codeur absolu.

Module de puissance

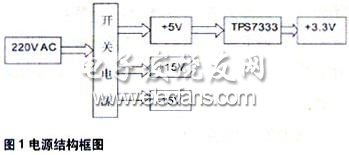

Le module d'alimentation se compose d'un circuit d'alimentation de commutation et d'une puce d'alimentation DC / DC, comme le montre la figure 1.

L'alimentation de commutation sur la figure convertit la tension de la grille AC 220V en + 5V, + 15V, -15V. L'alimentation de commutation peut filtrer diverses interférences dans le réseau électrique, et le transformateur dans l'alimentation de commutation sera 220 V et la sortie est + 5V, + 15V, -15V est isolée, le circuit interne utilise également TL431 pour ajuster le réglage La largeur d'impulsion de conduction du tube de l'interrupteur, de sorte que la régulation anti-infirmière, la sécurité, la stabilité et la tension de l'alimentation de l'alimentation de commutation est meilleure. Le TPS7333 est une puce DC / DC. La tension CC + 5V est convertie en une tension à courant continu stable de + 3,3V pour une utilisation par le CPLD. Le TPS7333 a une meilleure efficacité de conversion, la fiabilité et la régulation de tension. Il peut être utilisé dans la plage de tension de + 3,77 V- + 10V. La conversion + 3,3 V entraîne une brûlure du CPLD car la tension d'entrée est trop élevée.

CPLD et ses modules de circuit périphérique

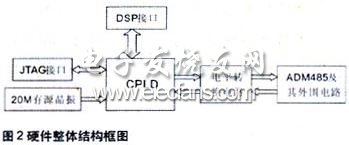

Le CPLD et ses modules de circuit périphérique sont principalement composés de CPLD, du circuit d'interface de téléchargement CPLD (interface JTAG), du circuit d'interface DSP, de l'oscillateur en cristal actif, du circuit de conversion de niveau et de l'ADM485 et de ses circuits périphériques (circuit d'interface responsable de la communication avec l'encodeur) . Figure 2).

Cette conception CPLD utilise EPM570T144C5 d'Altera, qui appartient à Max II d'Altera. Max II est un coût plus faible que Max I et consomme moins de puissance. L'appareil a plus de macro et le retard de l'appareil est contrôlé dans les 6 ns. Avec des performances à coût élevé, l'EPM570T144C5 compte 570 macrocellules. Le nombre d'épingles sur la puce est de 144, dont 116 sont des ports d'E / S disponibles, donc les ressources de cette puce sont suffisantes. Le CPLD est principalement responsable de la communication série à grande vitesse avec le codeur absolu et est contrôlé par la commande DSP pour transférer les données de l'encodeur et d'autres informations au DSP en parallèle.

L'interface JTAG est principalement utilisée pour télécharger le fichier exécutable sur le CPLD, installer l'environnement de développement de la société Altera - Quartus II sur le PC et compiler le programme VHDL écrit dans cet environnement de développement pour s'assurer que la compilation n'est pas sans erreur sans erreur et la fonction est implémentée. Connectez le câble de téléchargement à l'interface JTAG et téléchargez la carte CPLD via l'outil de téléchargement de programmation fourni par Quartus II.

L'interface DSP se compose de 8 lignes de données, 3 lignes d'adresse et 1 ligne de contrôle. Les 8 lignes de données sont responsables du transfert des données de l'encodeur et d'autres informations. Les 3 lignes d'adresse sont responsables de la transmission des commandes DSP et du décodage à la borne CPLD. Le CPLD transmet les données de l'encodeur ou d'autres informations au DSP via 8 lignes de données selon la commande décodée. La ligne de commande complète principalement le contrôle synchrone du CPLD et du DSP.

L'oscillateur à cristal actif de 20 m fournit principalement une horloge de référence pour le CPLD. Sous la conduite du signal d'horloge, le CPLD génère un débit en bauds de 2,5 Mo / s pour communiquer avec l'encodeur et génère une horloge Hz de 10 m pour certains signaux de contrôle logique. Fournir une fréquence d'horloge de 20 M Hz nécessite une tension CC de 3,3 V à partir de l'alimentation.

Le circuit de décalage de niveau est principalement responsable de la conversion de 3,3 V en 5 V ou 5V en 3,3 V, car les ports du noyau et des E / S du CPLD nécessitent une tension d'alimentation de 3,3 V, ce qui est requis pour ADM485 et encodeurs absolus. La tension d'alimentation et le circuit du conducteur du port d'E / S sont 5V, il est donc nécessaire de convertir 3,3 V en 5V ou 5V à 3,3 V avec la puce de conversion de niveau LVC4245A.

ADM485 et ses circuits périphériques sont la connexion matérielle entre CPLD et la communication à grande vitesse de l'encodeur absolu. La tension de travail d'ADM485 est de 5V et sa vitesse de communication maximale est de 5 Mo / s. L'utilisation de deux puces ADM485 pour la communication d'amarrage peut améliorer la capacité d'anti-interférence sur la ligne de communication, et la distance de transmission la plus longue peut atteindre 1,2 km. Le circuit périphérique est illustré à la figure 3. La moitié droite de la ligne pointillée appartient au circuit périphérique du codeur absolu. Les résistances de traction et de traction sont de 1k ohms, la résistance limitant de courant est de 220 ohms et le SDAT ADM485 est la broche de sortie de données. ADM485 est SRQ est la broche d'entrée de données, DE de ADM485 est la broche de commande externe, cette broche est contrôlée par CPLD. Étant donné que le protocole de communication RS-485 est à moitié duplex, ADM485 ne peut être que dans l'état d'envoi de données ou de recevoir des données. Lorsque ADM485 est de High, ADM485 est dans l'état de sortie des données (c'est-à-dire que CPLD reçoit des données). Lorsque DE OF ADM485 est à faible niveau, ADM485 est à l'état d'entrée de données (c'est-à-dire que CPLD envoie des données).

Partager sur:

Envoyer Une Demande

Ms. carol Dong

Numéro De Téléphone:86-431-85543703

Fax:86-431---88634119

Portable:+8613894866263

E-mail :sales@encoders.com.cn

Adresse De Compagnie:333Feiyue Donglu, Changchun City, Jilin Province. China, Changchun, Jilin

site mobile

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Fill in more information so that we can get in touch with you faster

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.